- 品牌

- Nvidia

- 型号

- H100

- 磁盘阵列

- Raid10

- CPU类型

- Intel Platinum 8558 48 核

- CPU主频

- 2.10

- 内存类型

- 64G

- 硬盘容量

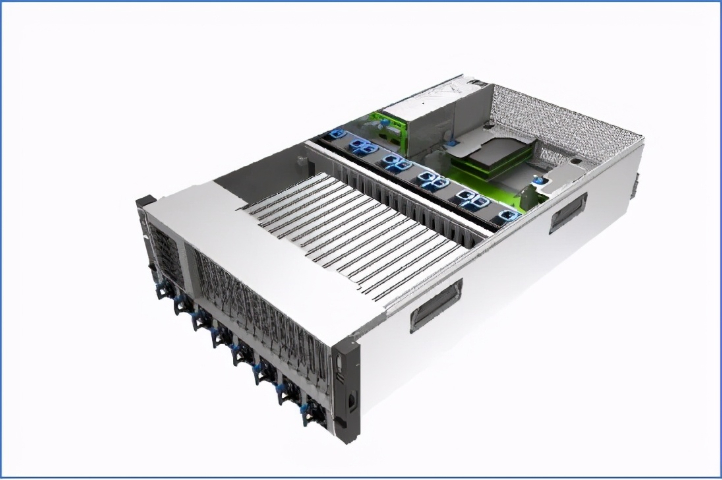

- Samsung PM9A3 7.6TB NVMe *8

- 厂家

- SuperMicro

- 标配CPU个数

- 2个

- 最大CPU个数

- 4个

- 内存容量

- 64G*32

- GPU

- 8 H100 80GB NVlink

使用张量维度和块坐标来定义数据传输,而不是每个元素寻址。TMA操作是异步的,利用了基于共享内存的异步屏障。TMA编程模型是单线程的,选择一个经线程中的单个线程发出一个异步TMA操作(cuda::memcpy_async)来复制一个张量,随后多个线程可以在一个cuda::barrier上等待完成数据传输。H100SM增加了硬件来加速这些异步屏障等待操作。TMA的一个主要***是它可以使线程自由地执行其他的工作。在Hopper上,TMA包揽一切。单个线程在启动TMA之前创建一个副本描述符,从那时起地址生成和数据移动在硬件中处理。TMA提供了一个简单得多的编程模型,因为它在复制张量的片段时承担了计算步幅、偏移量和边界计算的任务。异步事务屏障(“AsynchronousTransactionBarrier”)异步屏障:-将同步过程分为两步。①线程在生成其共享数据的一部分时发出"到达"的信号。这个"到达"是非阻塞的。因此线程可以自由地执行其他的工作。②终线程需要其他所有线程产生的数据。在这一点上,他们做一个"等待",直到每个线程都有"抵达"的信号。-***是允许提前到达的线程在等待时执行的工作。-等待的线程会在共享内存中的屏障对象上自转(spin)。H100 GPU 优惠销售,机会难得。技嘉H100GPU促销价

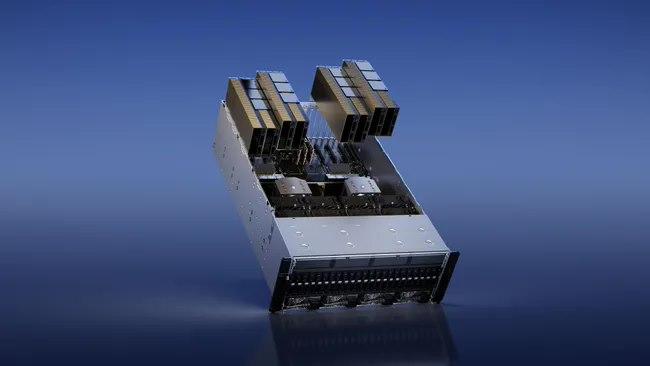

第四代NVIDIANVLink在全归约操作上提供了3倍的带宽提升,在7倍PCIeGen5带宽下,为多GPUIO提供了900GB/sec的总带宽,比上一代NVLink增加了50%的总带宽。第三代NVSwitch技术包括驻留在节点内部和外部的交换机,用于连接服务器、集群和数据中心环境中的多个GPU。节点内部的每个NVSwitch提供64个第四代NVLink链路端口,以加速多GPU连接。交换机的总吞吐率从上一代的。新的第三代NVSwitch技术也为多播和NVIDIASHARP网络内精简的集群操作提供了硬件加速。新的NVLinkSwitch系统互连技术和新的基于第三代NVSwitch技术的第二级NVLink交换机引入地址空间隔离和保护,使得多达32个节点或256个GPU可以通过NVLink以2:1的锥形胖树拓扑连接。这些相连的节点能够提供TB/sec的全连接带宽,并且能够提供难以置信的一个exaFlop(百亿亿次浮点运算)的FP8稀疏AI计算。PCIeGen5提供了128GB/sec的总带宽(各个方向上为64GB/s),而Gen4PCIe提供了64GB/sec的总带宽(各个方向上为32GB/sec)。PCIeGen5使H100可以与性能高的x86CPU和SmartNICs/DPU(数据处理单元)接口。LenovoH100GPU库存。对于开发者来说,H100 GPU 的稳定性和高能效为长时间的开发和测试提供了可靠保障.

稀疏性特征利用了深度学习网络中的细粒度结构化稀疏性,使标准张量性能翻倍。新的DPX指令加速了动态规划算法达到7倍。IEEEFP64和FP32的芯片到芯片处理速率提高了3倍(因为单个SM逐时钟(clock-for-clock)性能提高了2倍;额外的SM数量;更快的时钟)新的线程块集群特性(ThreadBlockClusterfeature)允许在更大的粒度上对局部性进行编程控制(相比于单个SM上的单线程块)。这扩展了CUDA编程模型,在编程层次结构中增加了另一个层次,包括线程(Thread)、线程块(ThreadBlocks)、线程块集群(ThreadBlockCluster)和网格(Grids)。集群允许多个线程块在多个SM上并发运行,以同步和协作的获取数据和交换数据。新的异步执行特征包括一个新的张量存储加速(TensorMemoryAccelerator,TMA)单元,它可以在全局内存和共享内存之间非常有效的传输大块数据。TMA还支持集群中线程块之间的异步拷贝。还有一种新的异步事务屏障,用于进行原子数据的移动和同步。新的Transformer引擎采用专门设计的软件和自定义Hopper张量技术相结合的方式。Transformer引擎在FP8和16位计算之间进行智能管理和动态选择,在每一层中自动处理FP8和16位之间的重新选择和缩放。

ITMALL.sale 非常重视客户反馈,并不断改进其服务和产品质量。通过定期回访和客户满意度调查,ITMALL.sale 了解客户在使用 H100 GPU 过程中的需求和建议,及时解决客户遇到的问题。ITMALL.sale 还设有专门的客户服务中心,提供7x24小时的在线支持和电话咨询,确保客户在任何时候都能够获得帮助。ITMALL.sale 的目标是通过不断优化服务,提升客户满意度,成为客户心中值得信赖的 H100 GPU 供应商。ITMALL.sale 的客户服务团队经过严格培训,具备专业的技术知识和良好的服务态度,能够为客户提供全的支持和帮助。H100 GPU 提供高效的视频编辑支持。

因此线程可以自由地执行其他**的工作。②终线程需要其他所有线程产生的数据。在这一点上,他们做一个"等待",直到每个线程都有"抵达"的信号。-***是允许提前到达的线程在等待时执行**的工作。-等待的线程会在共享内存中的屏障对象上自转(spin)(我理解的就是这些等待的线程在等待的时候无法执行其他工作)也是一个分裂的屏障,但不对到达的线程计数,同时也对事务进行计数。为写入共享内存引入一个新的命令,同时传递要写入的数据和事务计数。事务计数本质上是对字节计数异步事务屏障会在W**t命令处阻塞线程,直到所有生产者线程都执行了一个Arrive,所有事务计数之和达到期望值。异步事务屏障是异步内存拷贝或数据交换的一种强有力的新原语。集群可以进行线程块到线程块通信,进行隐含同步的数据交换,集群能力建立在异步事务屏障之上。H100HBM和L2cache内存架构HBM存储器由内存堆栈组成,位于与GPU相同的物理封装上,与传统的GDDR5/6内存相比,提供了可观的功耗和面积节省,允许更多的GPU被安装在系统中。H100 GPU 的基础时钟频率为 1410 MHz。北京H100GPU折扣

H100 GPU 在云计算中的应用也非常多。技嘉H100GPU促销价

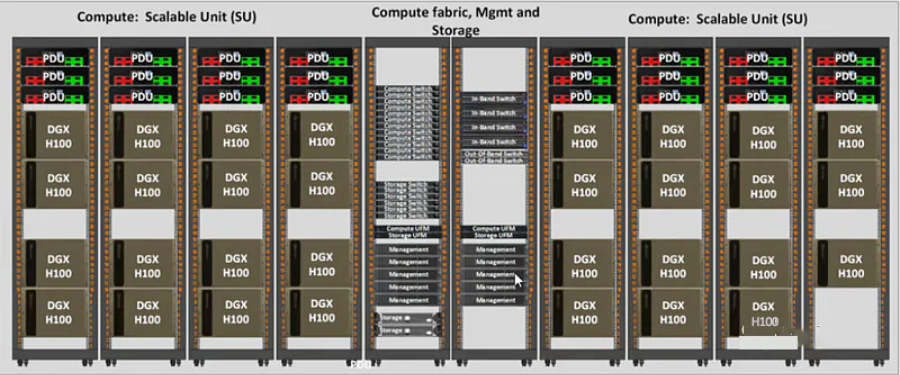

提供了1exaFLOP的FP8稀疏AI计算性能。同时支持无线带宽(InifiniBand,IB)和NVLINKSwitch网络选项。HGXH100通过NVLink和NVSwitch提供的高速互连,HGXH100将多个H100结合起来,使其能创建世界上强大的可扩展服务器。HGXH100可作为服务器构建模块,以集成底板的形式在4个或8个H100GPU配置中使用。H100CNXConvergedAcceleratorNVIDIAH100CNX将NVIDIAH100GPU的强大功能与NVIDIA®ConnectX-7SmartNIC的**组网能力相结合,可提供高达400Gb/s的带宽包括NVIDIAASAP2(加速交换和分组处理)等创新功能,以及用于TLS/IPsec/MACsec加密/的在线硬件加速。这种独特的架构为GPU驱动的I/O密集型工作负载提供了前所未有的性能,如在企业数据中心进行分布式AI训练,或在边缘进行5G信号处理等。H100GPU架构细节异步GPUH100扩展了A100在所有地址空间的全局共享异步传输,并增加了对张量内存访问模式的支持。它使应用程序能够构建端到端的异步管道,将数据移入和移出芯片,完全重叠和隐藏带有计算的数据移动。CUDA线程只需要少量的CUDA线程来管理H100的全部内存带宽其他大多数CUDA线程可以专注于通用计算,例如新一代TensorCores的预处理和后处理数据。扩展了层次结构。技嘉H100GPU促销价

- 超微H100GPU库存 2024-11-15

- DubaiH100GPU价格 2024-11-15

- QatarH100GPU库存 2024-11-15

- DubaiNVLINKH100GPU 2024-11-15

- 技嘉H100GPU促销 2024-11-15

- 重庆H100GPU总代 2024-11-15

- 香港H100GPU price 2024-11-15

- 重庆超微H100GPU 2024-11-15

- IranH100GPU促销 2024-11-15

- NVLINKH100GPU 2024-11-14

- LenovoH100GPU库存 2024-11-14

- xfusionH100GPU price 2024-11-14