- 品牌

- 云茂

- 型号

- 齐全

- 封装形式

- B***GA,CSP,QFP/PFP,MCM,SDIP,SOP/SOIC,PLCC,TSOP,TQFP,PQFP,SMD,DIP

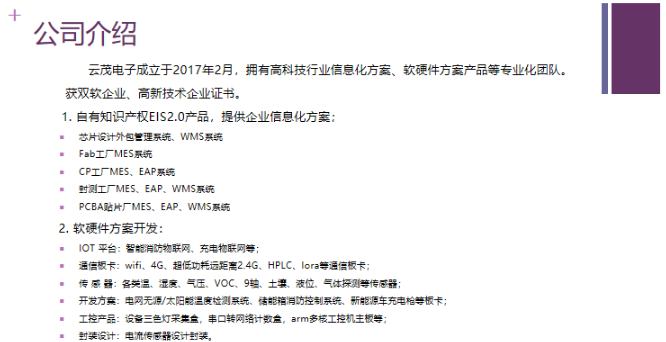

SiP芯片成品的制造过程,系统级封装(SiP)技术种类繁多,本文以双面塑封SiP产品为例,简要介绍SiP芯片成品的制造过程。SiP封装通常在一块大的基板上进行,每块基板可以制造几十到几百颗SiP成品。无源器件贴片,倒装芯片封装(Flip Chip)贴片——裸片(Die)通过凸点(Bump)与基板互连,回流焊接(正面)——通过控制加温熔化封装锡膏达到器件与基板间的键合焊线,键合(Wire Bond)——通过细金属线将裸片与基板焊盘连接塑封(Molding)——注入塑封材料包裹和保护裸片及元器件。SiP 在应用终端产品领域(智能手表、TWS、手机、穿戴式产品、智能汽车)的爆发点也将愈来愈近。贵州芯片封装方式

通信SiP 在无线通信领域的应用较早,也是应用较为普遍的领域。在无线通讯领域,对于功能传输效率、噪声、体积、重量以及成本等多方面要求越来越高,迫使无线通讯向低成本、便携式、多功能和高性能等方向发展。SiP 是理想的解决方案,综合了现有的芯核资源和半导体生产工艺的优势,降低成本,缩短上市时间,同时克服了 SOC 中诸如工艺兼容、信号混合、噪声干扰、电磁干扰等难度。手机中的射频功放,集成了频功放、功率控制及收发转换开关等功能,完整地在 SiP 中得到了解决。广东MEMS封装参考价预计到2028年,SiP系统级封装市场总收入将达到338亿美元,年复合增长率为8.1%。

较终的SiP是什么样子的呢?理论上,它应该是一个与外部没有任何连接的单独组件。它是一个定制组件,非常适合它想要做的工作,同时不需要外部物理连接进行通信或供电。它应该能够产生或获取自己的电力,自主工作,并与信息系统进行无线通信。此外,它应该相对便宜且耐用,使其能够在大多数天气条件下运行,并在发生故障时廉价更换。随着对越来越简化和系统级集成的需求,这里的组件将成为明天的SiP就绪组件,而这里的SiP将成为子系统级封装(SSiP)。SiP就绪组件和SSiP将被集成到更大的SiP中,因为系统集成使SiP技术越来越接近较终目标:较终SiP。

SiP具有以下优势:降低成本 – 通常伴随着小型化,降低成本是一个受欢迎的副作用,尽管在某些情况下SiP是有限的。当对大批量组件应用规模经济时,成本节约开始显现,但只限于此。其他可能影响成本的因素包括装配成本、PCB设计成本和离散 BOM(物料清单)开销,这些因素都会受到很大影响,具体取决于系统。良率和可制造性 – 作为一个不断发展的概念,如果有效地利用SiP专业知识,从模塑料选择,基板选择和热机械建模,可制造性和产量可以较大程度上提高。SOC与SIP都是将一个包含逻辑组件、内存组件、甚至包含无源组件的系统,整合在一个单位中。

SiP整体制程囊括了着晶、打线、主/被动组件SMT及塑封技术,封装成型可依据客户设计制作不同形状模块,甚至是3D立体结构,藉此可将整体尺寸缩小,预留更大空间放置电池,提供更大电力储存,延长产品使用时间,但功能更多、速度更快,因此特别适用于射频相关应用如5G毫米波模块、穿戴式装置及汽车电子等领域。微小化制程三大关键技术,在设计中元器件的数量多寡及排布间距,即是影响模块尺寸的较主要关键。要能够实现微小化,较重要的莫过于三项制程技术:塑封、屏蔽及高密度打件技术。随着集成的功能越来越多,PCB承载的功能将逐步转移到SIP芯片上。湖北模组封装

SiP模组是一个功能齐全的子系统,它将一个或多个IC芯片及被动元件整合在一个封装中。贵州芯片封装方式

SIP工艺解析:装配焊料球,目前业内采用的植球方法有两种:“锡膏”+“锡球”和“助焊膏”+“锡球”。(1)“锡膏”+“锡球”,具体做法就是先把锡膏印刷到BGA的焊盘上,再用植球机或丝网印刷在上面加上一定大小的锡球。(2)“助焊膏”+“锡球”,“助焊膏”+“锡球”是用助焊膏来代替锡膏的角色。分离,为了提高生产效率和节约材料,大多数SIP的组装工作都是以阵列组合的方式进行,在完成模塑与测试工序以后进行划分,分割成为单个的器件。划分分割主要采用冲压工艺。贵州芯片封装方式

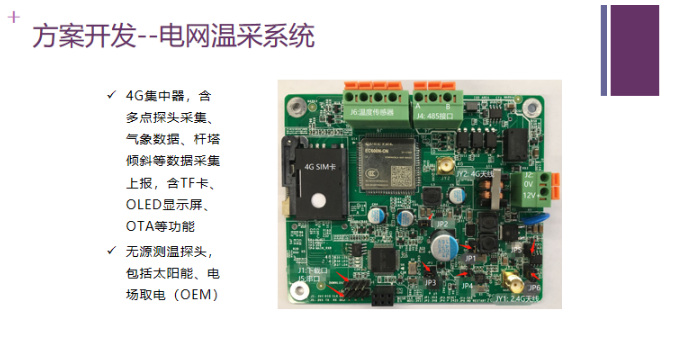

面对客户在系统级封装产品的设计需求,云茂电子具备完整的数据库,可在整体微小化的基础上,提供料件及设计的较佳解,接着开始进行电路布局(Layout) 与构装(Structure)设计。经过封装技术,将整体电路及子系统塑封在一个光「芯片」大小的模块。 高密度与高整合的模块化设计前期的模拟与验证特别至关重要,云茂电子提供包含载板设计和翘曲仿真、电源/讯号完整性分析(PI/SI)、热流模拟分析(Thermal)等服务确保模块设计质量。实验室内同时也已经为系统整合验证建置完整设备,协助客户进行模块打件至主板后的射频校准测试与通讯协议验证,并提供系统级功能性与可靠度验证。 Sip这种创新性的系统...

- 湖北MCU SIP封装 2024-11-13

- 安徽半导体芯片封装定制 2024-11-13

- 湖北芯片封装型式 2024-11-12

- 山东BGA封装行价 2024-11-12

- 广西MEMS封装技术 2024-11-11

- 浙江陶瓷封装参考价 2024-11-10

- 天津半导体芯片封装价格 2024-11-10

- 山东芯片封装行价 2024-11-09

- 河南MEMS封装测试 2024-11-09

- 贵州MEMS封装方式 2024-11-09

- 上海WLCSP封装流程 2024-11-07

- 湖南COB封装 2024-11-06

- 浙江IPM封装服务商 2024-11-06

- 广东COB封装定制 2024-11-06

- 贵州芯片封装方式 2024-11-06

- 浙江SIP封装市场价格 2024-11-05

- 广东PCBA产品方案策划 11-13

- 南通视频监控产品方案厂家 11-13

- 湖北MCU SIP封装 11-13

- 安徽半导体芯片封装定制 11-13

- 湖北芯片封装型式 11-12

- 山东BGA封装行价 11-12

- 北京电子手表产品方案服务商 11-12

- 天津物联网电子产品方案定制价格 11-12

- 山西专业电子产品方案设计公司 11-12

- 安徽电力高压线无源测温产品方案参考价 11-12