- 品牌

- 云茂

- 型号

- 齐全

- 封装形式

- B***GA,CSP,QFP/PFP,MCM,SDIP,SOP/SOIC,PLCC,TSOP,TQFP,PQFP,SMD,DIP

SiP还具有以下更多优势:降低成本 – 通常伴随着小型化,降低成本是一个受欢迎的副作用,尽管在某些情况下SiP是有限的。当对大批量组件应用规模经济时,成本节约开始显现,但只限于此。其他可能影响成本的因素包括装配成本、PCB设计成本和离散 BOM(物料清单)开销,这些因素都会受到很大影响,具体取决于系统。良率和可制造性 – 作为一个不断发展的概念,如果有效地利用SiP专业知识,从模塑料选择,基板选择和热机械建模,可制造性和产量可以较大程度上提高。先进封装对于精度的要求非常高,因为封装中的芯片和其他器件的尺寸越来越小,而封装密度却越来越大。江西IPM封装哪家好

SiP的未来趋势和事例。人们可以将SiP总结为由一个衬底组成,在该衬底上将多个芯片与无源元件组合以创建一个完整的功能单独封装,只需从外部连接到该封装即可创建所需的产品。由于由此产生的尺寸减小和紧密集成,SiP在MP3播放器和智能手机等空间受限的设备中非常受欢迎。另一方面,如果只要有一个组件有缺陷,整个系统就会变得无法正常工作,从而导致制造良率下降。尽管如此,推动SiP更多开发和生产的主要驱动力是早期的可穿戴设备,移动设备和物联网设备市场。在当前的SiP限制下,需求仍然是可控的,其数量低于成熟的企业和消费类SoC市场。天津BGA封装技术SiP是使用成熟的组装和互连技术,把各种集成电路器件集成到一个封装体内,实现整机系统的功能。

SIP优点:1、高生产效率,通过SIP里整合分离被动元件,降低不良率,从而提高整体产品的成品率。模组采用高阶的IC封装工艺,减少系统故障率。2、简化系统设计,SIP将复杂的电路融入模组中,降低PCB电路设计的复杂性。SIP模组提供快速更换功能,让系统设计人员轻易加入所需功能。3、成本低,SIP模组价格虽比单个零件昂贵,然而PCB空间缩小,低故障率、低测试成本及简化系统设计,使总体成本减少。4、简化系统测试,SIP模组出货前已经过测试,减少整机系统测试时间。

SiP 封装优势:1)封装面积增大,SiP在同一个封装种叠加两个或者多个芯片。把垂直方向的空间利用起来,同时不必增加引出管脚,芯片叠装在同一个壳体内,整体封装面积较大程度上减少。2)采用超薄的芯片堆叠与TSV技术使得多层芯片的堆叠封装体积减小,先进的封装技术可以实现多层芯片堆叠厚度。3)所有元件在一个封装壳体内,缩短了电路连接,见笑了阻抗、射频、热等损耗影响。提高了光,电等信号的性能。4)SiP 可将不同的材料,兼容不同的GaAs,Si,InP,SiC,陶瓷,PCB等多种材料进行组合进行一体化封装。SiP封装方法的应用领域逐渐扩展到工业控制、智能汽车、云计算、医疗电子等许多新兴领域。

SMT制程在SIP工艺流程中的三部分都有应用:1st SMT PCB贴片 + 3rd SMT FPC贴镍片 + 4th SMT FPC+COB。SiP失效模式和失效机理,主要失效模式:(1) 焊接异常:IC引脚锡渣、精密电阻连锡。Ø 原因分析:底部UF (Underfill底部填充)胶填充不佳,导致锡进入IC引脚或器件焊盘间空洞造成短路。(2) 机械应力损伤:MOS芯片、电容裂纹。Ø 原因分析:(1) SiP注塑后固化过程产生的应力;(2)设备/治具产生的应力。(3) 过电应力损伤:MOS、电容等器件EOS损伤。Ø 原因分析:PCM SiP上的器件受电应力损伤(ESD、测试设备浪涌等)。SiP 封装采用超薄的芯片堆叠与TSV技术使得多层芯片的堆叠封装体积减小。安徽SIP封装方案

SIP板身元件尺寸小,密度高,数量多,传统贴片机配置难以满足其贴片要求。江西IPM封装哪家好

SiP具有以下优势:可靠性 – 由于SiP与使用分立元件(如IC或无源器件)的PCB系统非常相似,因此它们至少具有相同的预期故障概率。额外的可靠性来自所涉及的封装,这可以增强系统并为设备提供更长的使用寿命。一个例子是使用模塑来封装系统,从而保护焊点免受物理应力的影响。天线集成 – 在许多无线应用(蓝牙、WiFi)中,都需要天线。在系统级封装解决方案中,天线可以集成到封装中,与RF IC的距离非常短,从而确保无线解决方案的更高性能。江西IPM封装哪家好

3D SIP。3D封装和2.5D封装的主要区别在于:2.5D封装是在Interposer上进行布线和打孔,而3D封装是直接在芯片上打孔和布线,电气连接上下层芯片。3D集成目前在很大程度上特指通过3D TSV的集成。物理结构:所有芯片及无源器件都位于XY平面之上且芯片相互叠合,XY平面之上设有贯穿芯片的TSV,XY平面之下设有基板布线及过孔。电气连接:芯片采用TSV与RDL直接电连接。3D集成多适用于同类型芯片堆叠,将若干同类型芯片竖直叠放,并由贯穿芯片叠放的TSV相互连接而成,见下图。类似的芯片集成多用于存储器集成,如DRAM Stack和FLASH Stack。通信SiP在无线通信领域的应用...

- 南通COB封装流程 2024-09-19

- 四川系统级封装服务商 2024-09-19

- 南通MEMS封装价位 2024-09-18

- 吉林半导体芯片封装技术 2024-09-18

- 广西IPM封装价位 2024-09-18

- 河南系统级封装型式 2024-09-15

- 河南MEMS封装服务商 2024-09-14

- 山西陶瓷封装精选厂家 2024-09-12

- 河北系统级封装工艺 2024-09-11

- 上海半导体芯片封装价位 2024-09-11

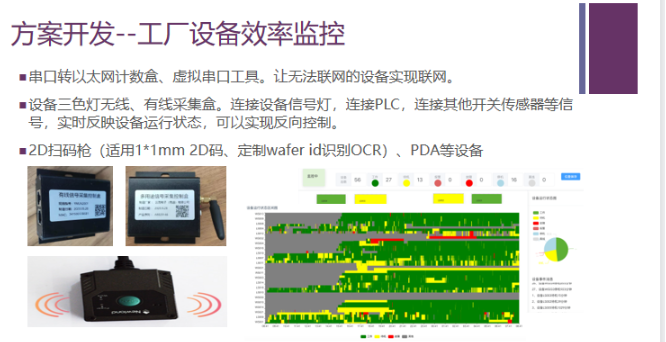

- 江苏HPLC电力抄表产品方案策划 09-19

- 四川系统级封装服务商 09-19

- 湖南PCBA贴片厂MES系统价格 09-19

- 天津PCBA贴片厂EAP系统价位 09-19

- 湖南PCBA贴片厂EAP系统参考价 09-19

- 河南专业特种封装供应商 09-18

- 南通MEMS封装价位 09-18

- 湖南Fab工厂MES系统市价 09-18

- 浙江多用途信号采集控制盒产品方案 09-18

- 吉林半导体芯片封装技术 09-18