- 品牌

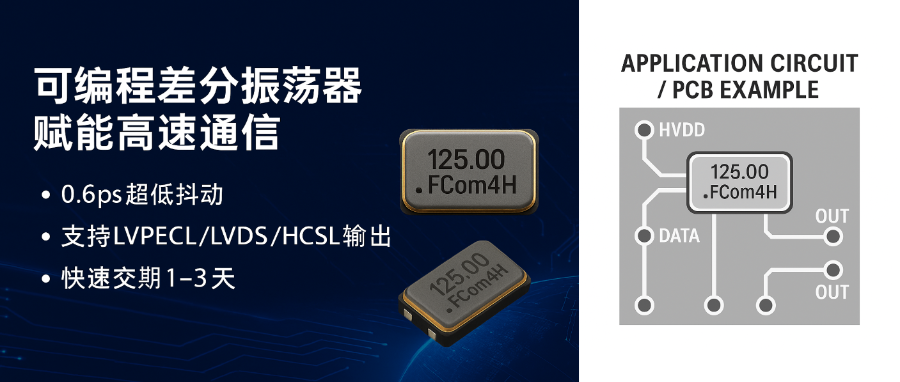

- FCom富士晶振

- 型号

- FCO-L-PG

- 系列

- FCO-L-PG

- 类型

- MHz晶体

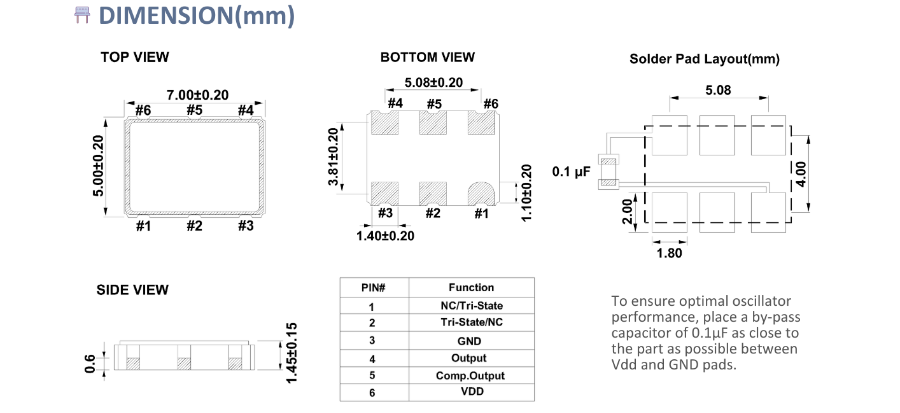

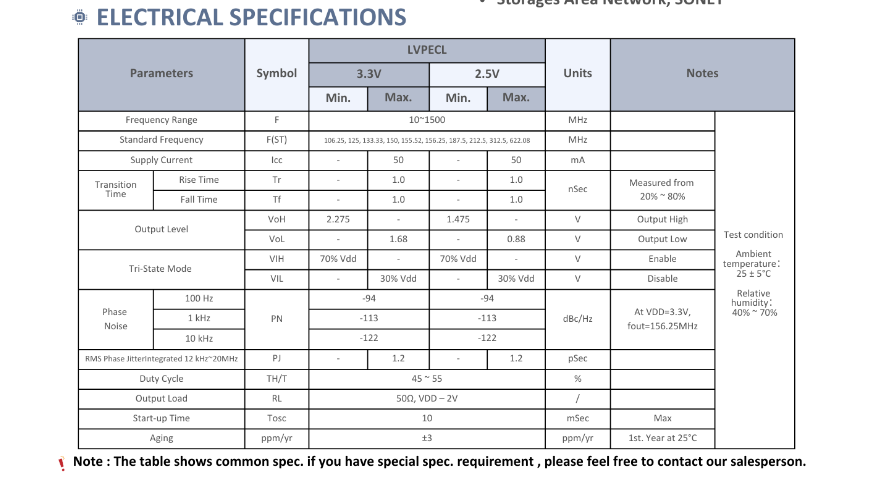

- 频率范围

- 10 MHz ~ 220 MHz

- 工作电压

- 1.8V / 2.5V / 3.3V 可选

- 温度频差

- ±25ppm / ±50ppm(出厂可选)

- 工作温度

- –40°C ~ +105°C

- 相位抖动

- 0.2 ~ 0.6ps RMS(12kHz~20MHz)

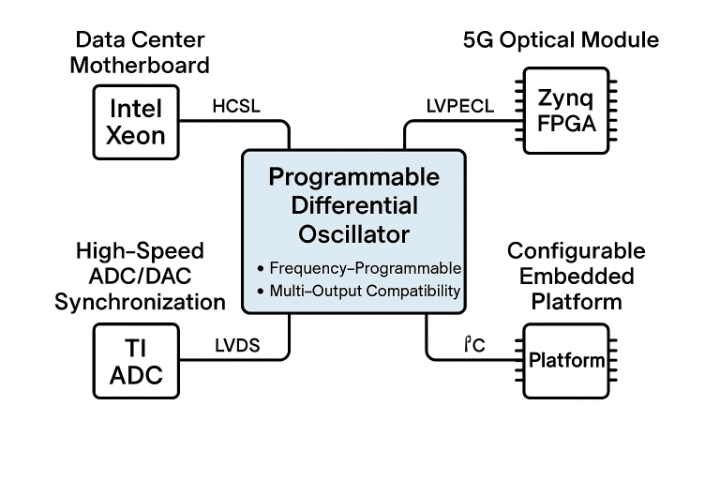

智能交通控制系统中的时钟标准化建设 智能交通控制系统集成车路协同、信号灯管理、视频识别、边缘计算等多种功能,对设备间的时钟同步与模块间的数据一致性提出了严格要求。尤其是在多源图像融合、车道识别、红绿灯自适应调度等环节,要求系统中每个子模块都具备高稳定性、低延迟、精确同步的时钟输入。FCom富士晶振推出的可编程差分振荡器正适用于构建统一时钟管理平台,为智能交通系统提供强力支撑。 产品支持24MHz、27MHz、74.25MHz、100MHz、125MHz等频率配置,输出格式为LVDS/HCSL/CMOS,能够驱动信号控制器、AI摄像模块、交通协调通信模块与图像融合主控板等关键设备。可编程特性支持单颗振荡器输出多频点并统一启停管理,实现交通节点控制设备的时钟标准化部署。 在抗干扰方面,FCom产品通过多项电磁兼容性测试,在路侧设备高压闪断、无线电干扰与雷击浪涌环境下仍保持输出稳定,频率稳定度达±10ppm,极大保障交通信号的调度连续性。 产品封装适配车规级与工业级应用标准,适合于交通路口控制箱、高速ETC系统、智慧路侧站、信号协调中心等环境恶劣但时序要求严格的部署点。可编程差分振荡器已成为前沿通信平台的标准配置。高性能可编程差分振荡器类型

可编程差分振荡器

数字孪生工业仿真系统的同步驱动时钟支撑 数字孪生系统通过对工业物理系统的实时仿真建模与反馈控制,各个方面应用于智能制造、仿真测试台、设备虚拟调试等场景。其数据采集板、虚拟控制器、仿真同步处理模块之间要求极高的时间一致性与信号同步性。FCom富士晶振可编程差分振荡器提供低延迟、高频稳、多接口输出能力,满足复杂仿真场景对统一时钟架构的苛刻要求。 支持配置10MHz、25MHz、50MHz、100MHz、125MHz、200MHz等频点输出,支持多通道同步启停与输出格式配置,适配仿真模型核、输入激励模块、同步触发采样链路与FPGA板卡逻辑时钟。 其典型抖动0.05~0.1ps,频率切换时间小于5ms,支持数字接口配置多场景预设频率模板,是构建虚拟与物理系统之间“时间桥梁”的基础组件。 产品已部署于工业仿真云平台、PLC虚拟调试系统、装备预测性维护测试台与多物理场集成仿真平台中。高频稳定可编程差分振荡器生产企业通过外部EEPROM可自动加载可编程差分振荡器频点。

AI推理加速卡中的差分振荡器布局优化 随着AI训练与推理系统在数据中心各个方面部署,GPU/TPU/NPU加速卡成为高速计算任务的重要载体。这些加速模块内部包含高频SerDes链路、大容量高速缓存与高速接口(PCIe Gen4/Gen5、CXL、NVLink),其性能稳定性高度依赖于精确可靠的时钟信号。FCom富士晶振推出的可编程差分振荡器,特别适用于AI推理加速卡的时钟配置与性能优化。 FCom产品支持100MHz、125MHz、156.25MHz、200MHz、250MHz等高频点,可输出HCSL/LVDS/PECL等接口,具备0.1ps甚至低至0.05ps的RMS抖动能力,确保GPU之间的高速通道在高速传输中保持时钟一致性与低误码率。

卫星通信链路中的时钟同步保障方案 卫星通信系统在数据回传、信道调制、星地链路同步、波束成型等多个环节高度依赖参考时钟的稳定输出。由于空间环境中存在温漂、振动、辐射、电源波动等因素,可编程差分振荡器成为卫星通信中继器、地面接收站、星载调制板中常用的高可靠时钟器件。FCom富士晶振推出的差分输出型可编程晶振产品,凭借低抖动、高稳定性、高定制能力优势,成为行业首要之选。 FCom产品支持10MHz、20MHz、40MHz、100MHz、156.25MHz、200MHz等频率点,可通过预烧录或配置工具设定目标频率,输出接口可设为LVPECL/LVDS/CMOS,支持冗余热备份输出切换与温度补偿算法。 产品结构采用高密陶瓷封装,具备耐真空、抗冲击、防辐射特性,可在-55~+125°C工作条件下保持频率稳定,适合星载通信子系统与地面波束控制终端同步架构。 FCom可编程差分振荡器目前已成功应用于LEO通信星地中继、航空卫星电视平台、机载VSAT接入模块等系统中,为远距离无线通信提供强有力的时钟支撑。多频点测试平台推荐统一采用可编程差分振荡器。

工业级多节点同步系统对时钟精度的结构化依赖 工业自动化中如机械臂协调、智能输送系统、多传感器采集平台中,多个处理节点需依赖统一、低延迟、抗干扰的时钟源来维持任务同步。FCom富士晶振推出的可编程差分振荡器,为这种分布式控制系统提供精确、灵活、低抖动的同步时钟解决方案。 通过配置支持25MHz、50MHz、100MHz、125MHz、156.25MHz等频率输出,并兼容LVDS、HCSL等差分格式,可为以太网通信芯片、传感器接口模块、控制器之间建立统一频率框架。每个时钟输出通道均可配置启停逻辑与OE控制,从而在任务切换中进行动态时钟管理。选型灵活、配置便捷是可编程差分振荡器的突出优势。高频稳定可编程差分振荡器诚信合作

可编程差分振荡器适用于FPGA平台动态频率配置。高性能可编程差分振荡器类型

大规模FPGA设计项目中的统一时钟架构构建 在通信基站、图像处理平台、测试测量设备、AI网关等多个场景中,FPGA作为关键处理单元需同时管理多个时钟域(输入同步、IO驱动、PLL控制、AXI总线),设计中存在频率出错、资源浪费与同步偏移风险。FCom富士晶振可编程差分振荡器提供统一频率源与灵活配置方式,为大规模FPGA设计提供集中管理的可控时钟结构。 FCom产品支持多频输出(如24MHz、50MHz、100MHz、125MHz、156.25MHz、200MHz),具备LVDS/HCSL多接口配置能力,可连接至FPGA外部时钟输入口、IO Bank参考时钟、PLL Clock-IN与内部逻辑触发器。输出抖动低至0.1ps,保障时序余量。 通过FCom提供的GUI工具,用户可快速配置目标频率组合并仿真接口兼容性,提升工程调试效率。产品支持1.8V~3.3V工作平台,适应不同FPGA品牌(Xilinx、Intel、Lattice、Microchip等)IO电压标准。高性能可编程差分振荡器类型

- FCO-7L-PG可编程差分振荡器常见问题 2025-12-21

- 车规级可编程差分振荡器批量定制 2025-12-21

- 5032可编程差分振荡器厂家报价 2025-12-21

- 多输出可编程差分振荡器厂家报价 2025-12-20

- 国产可编程差分振荡器价格查询 2025-12-20

- 优势可编程差分振荡器订做价格 2025-12-20

- 高稳定可编程差分振荡器电话 2025-12-20

- 7050可编程差分振荡器诚信合作 2025-12-20

- 高频稳定可编程差分振荡器诚信合作 2025-12-20

- 高频可编程差分振荡器推荐厂家 2025-12-20

- 国产可编程差分振荡器怎么样 2025-12-19

- AEC-Q200可编程差分振荡器推荐厂家 2025-12-19